## **Instruction Manual**

## **Tektronix**

VX4820 Digital Test Module 070-8319-01

#### Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to the Safety Summary prior to performing service.

Please check for change information at the rear of this manual.

First Printing: April 1991 Revised Printing: August 1991 Copyright © Tektronix, Inc. 1991. All rights reserved.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

## **Table of Contents**

## **General Safety Summary**

#### **Preface**

| Section 1 | Purpose of this Document in Organization of this Manual in Notational Conventions in Active Signal States in Number Base in Related Publications in Section Se |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | Pin I/O Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           | Test PASS/FAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Test Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | Test Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | Test Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | Learn Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           | Backplane Triggers and Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|           | Systems of 128 — 768 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|           | Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | Standard Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | Optional Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Performance Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           | Definition of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Section 2 Preparation for Use

|               | Configuration                                  | 2-1 |

|---------------|------------------------------------------------|-----|

|               | Calculating System Power and Cooling           | 2-1 |

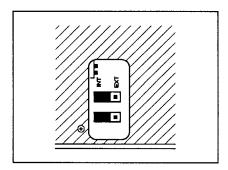

|               | Auxilary Pod Power                             | 2-1 |

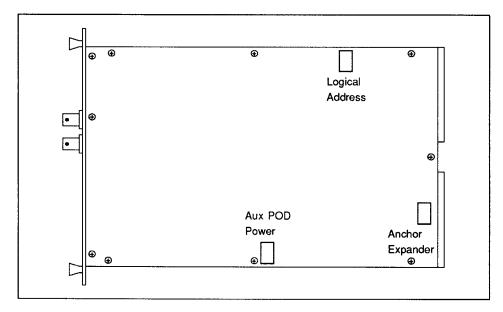

|               | Module Jumpers                                 | 2-2 |

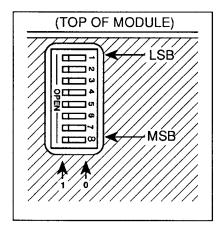

|               | Logical Address Switch                         | 2-3 |

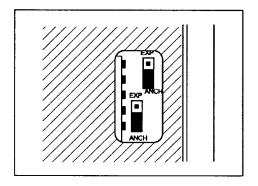

|               | Configuring the Backplane Jumpers              | 2-4 |

|               | GPIB Communications Terminator                 | 2-4 |

|               | Installation                                   | 2-5 |

|               | Module Installation Using Ejector Handles      | 2-5 |

|               | Module Removal Using Ejector Handles           | 2-5 |

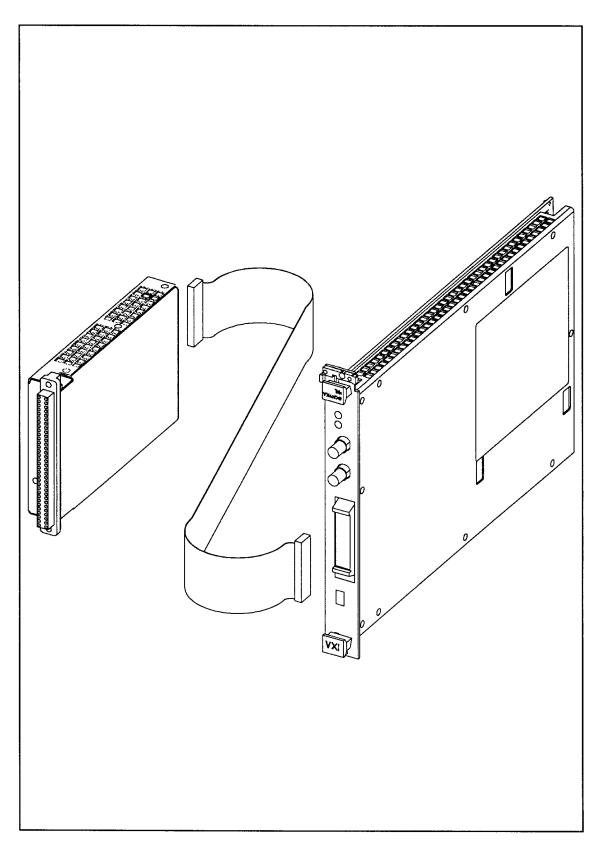

|               | Pod Cable Assembly                             | 2-5 |

|               | Group Calibration                              | 2-6 |

|               | Group Calibration Procedure                    | 2-6 |

|               | Internal Clock Calibration                     | 2-7 |

|               | Required Equipment                             |     |

|               | External Clock Calibration                     |     |

|               | Required Equipment                             | 2-9 |

| Section 5 Ope | eration and Programming                        |     |

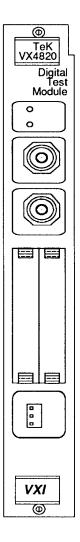

|               | Connectors and Indicators                      |     |

|               | Connectors                                     |     |

|               | Indicators                                     |     |

|               | Getting Started                                |     |

|               | Module Installation                            |     |

|               | Basic Communications                           |     |

|               | Exercising the Module I/O Pins                 |     |

|               | Writing a Simple Test                          |     |

|               | Retrieving Test Failure Data                   |     |

|               | Test Debug Support                             |     |

|               | Learn Mode                                     |     |

|               | Branching                                      |     |

|               | Using VXI STST Protocol                        |     |

|               | Multi-Module Systems                           |     |

|               | Multi-Module Systems Using an External Clock 3 |     |

|               | Diagnostics and Calibration                    | -14 |

| Section 4 Rea | ar Panel Interface                             |     |

|               |                                                | 4-1 |

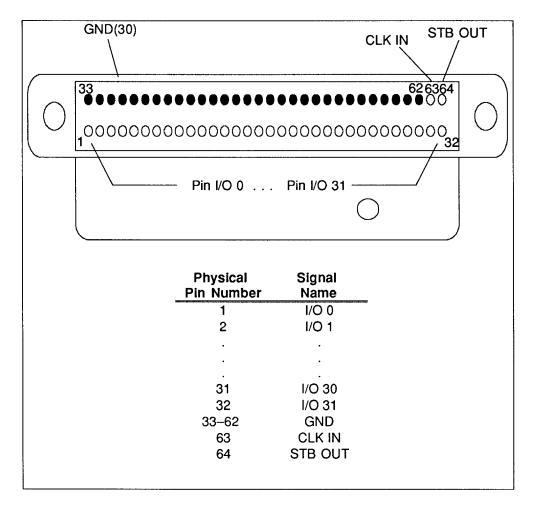

|               | P1 Pinout                                      | 4-2 |

|               | P2 Pinout                                      | 4-3 |

## **Section 5 Command Notation and Formats**

| Introduction                                           | 5-1  |

|--------------------------------------------------------|------|

| Command Notation                                       |      |

| Program Message                                        |      |

| ASCII Code                                             |      |

| Syntactic Delimiters                                   |      |

| White Space                                            |      |

| Special Characters                                     |      |

| Program Data                                           |      |

|                                                        |      |

| Numeric Program Data Value Range                       |      |

| Decimal Numeric Program Data                           |      |

| Non-Decimal Numeric Program Data                       |      |

| String Program Data                                    |      |

| Command Formats                                        |      |

| Simple Command Program Header                          |      |

| Simple Query Program Header                            |      |

| Compound Command Program Header                        | 5-7  |

| Compound Query Program Header                          |      |

| Common Command Program Header                          |      |

| Common Query Program Header                            |      |

| Multiple-Command Format With Same 1st Program Mnemonic |      |

|                                                        |      |

| Instrument Response Queuing                            |      |

| Case Sensitivity                                       |      |

| Command Types                                          |      |

| Command Dictionary Layout                              | 5-10 |

| Image du cations                                       |      |

| Introduction                                           |      |

| Alphabetical Command Listing                           |      |

| Functional Command Listing                             |      |

| ARM                                                    |      |

| BLRANGE                                                |      |

| CLKCAL                                                 |      |

| CONNECT                                                |      |

| CONTINUE                                               | 6-15 |

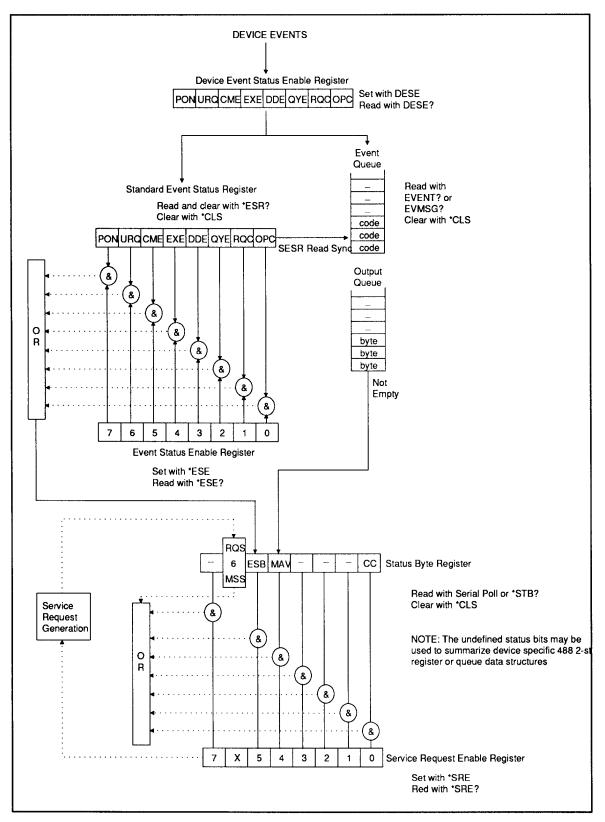

| DESE                                                   |      |

|                                                        | 6-17 |

| EVENT?                                                 |      |

| EVMSG?                                                 | 6-19 |

| FAILDATA?                                              | 6-20 |

| FAILPIN?                                               | 6-21 |

| GRPMODE                                                |      |

| HEADER                                                 | 6-24 |

| HELP?                                                  |      |

| IDPOD                                                  |      |

|                                                        | 6-27 |

| INIT                                                   |      |

| INTCLKRATE                                             |      |

| MODE                                                   |      |

| NEW                                                    |      |

| NEWPASS                                                | 6-33 |

|                                                        |      |

REV AUG 1991

|                | NVRECALL       6-34         NVSAVE       6-35         PASSWORD       6-36         PAUSE       6-37         PINTEST?       6-38         PODTYPE?       6-38         READPIN?       6-40         REPORT       6-41         SEQ       6-42         SINGLESTEP       6-56         START       6-57         STATE?       6-58         STERR?       6-58         STOP       6-60         TSTPAT       6-61         USER       6-62         WRITEPIN       6-63         WSLOAD       6-64 |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 7 Syst | tem Command Dictionary                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Section 8 Digi | tal Toolbox                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | What is required                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | Using Digital Toolbox                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | Generating Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | Modular Test Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | Downloading, Executing, and Debugging a Test 8-4                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | On-line Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

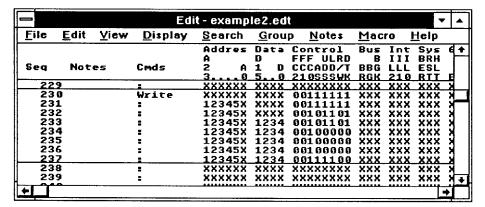

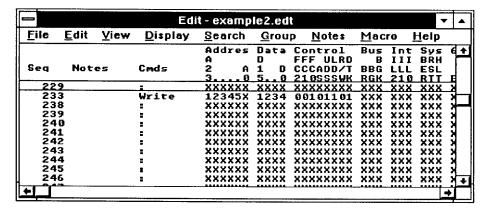

|                | EDIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | Starting the Editor                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

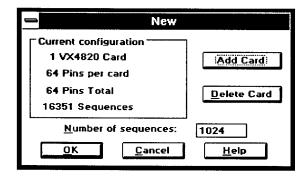

|                | Selecting the Test Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

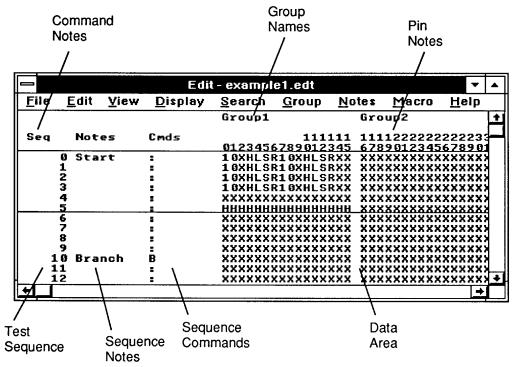

|                | Display Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | Display Formatting                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | Display Colors                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | Grouping Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | Changing Group Names                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | Hiding Pins or Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | Redisplaying Pins or Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Pin Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Sequence Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | Marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | Group Radix                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

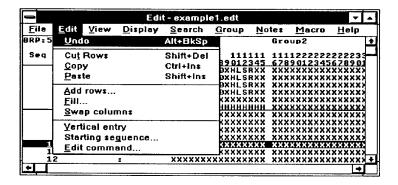

|                | Editing Test Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                | Typing Data in Binary Radix                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | Typing Data in Octal and Hey Radiy                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | Viewing Test Data                     | 8-11 |

|-----------|---------------------------------------|------|

|           | Copy and Paste Data                   |      |

|           |                                       |      |

|           | Cut, Copy, and Paste Test Sequences   |      |

|           | Fill Data Pattern                     |      |

|           | Swapping Pin Data                     | 8-13 |

|           | Find and Change                       | 8-13 |

|           | Selecting the Starting Sequence       |      |

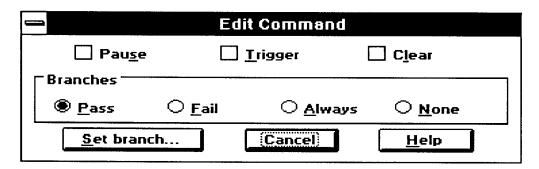

|           | Sequence Commands                     |      |

|           |                                       |      |

|           | Test Files                            |      |

|           | Saving and Retrieving Test Files      |      |

|           | Printing Test Files                   |      |

|           | Macros                                | 8-17 |

|           | Using Macros                          | 8-17 |

|           | Defining Macros                       |      |

|           | Macro File Example                    |      |

|           |                                       |      |

|           | Import and Export of ASCII Files      |      |

|           | VERIFY                                |      |

|           | Starting Verify                       | 8-22 |

|           | Checking Macro Files                  | 8-22 |

|           | MERGE                                 |      |

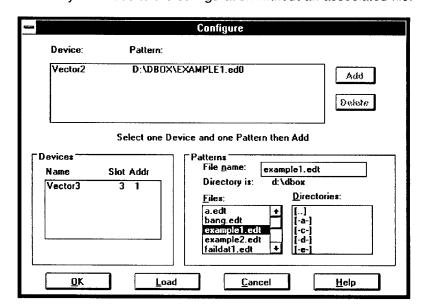

|           | STARTING THE MERGE UTILITY            | 8-23 |

|           | SELECTING INPUT FILES                 |      |

|           |                                       |      |

|           | Saving the Merge Configuration        |      |

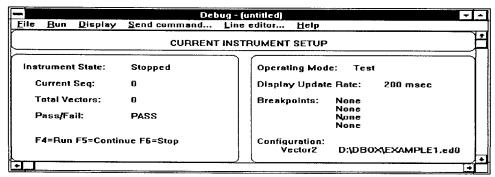

|           | DEBUG                                 |      |

|           | Starting the Loader/Debugger          | 8-24 |

|           | Configuring the Test                  | 8-24 |

|           | Downloading / Uploading Test Data     |      |

|           | Executing the Test                    |      |

|           | The Debug Display                     |      |

|           |                                       |      |

|           | Saving the Debug Configuration        |      |

|           | Trace Display                         |      |

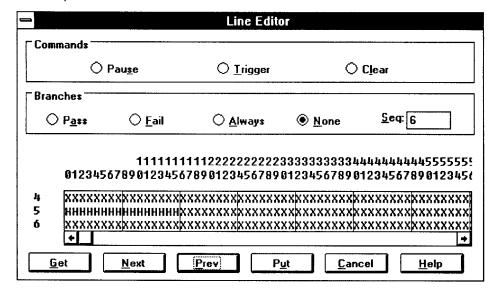

|           | Sequence Line Editor                  |      |

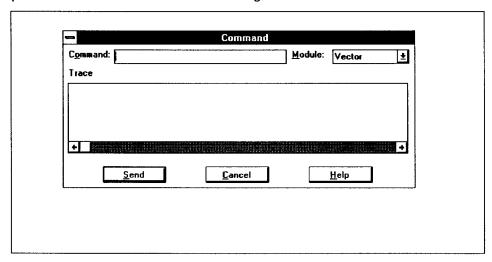

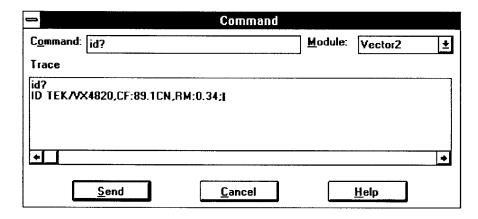

|           | Talker / Listener                     | 8-29 |

|           |                                       |      |

| Section 9 | Module Service                        |      |

|           | Conoral Information                   | 0.4  |

|           | General Information                   |      |

|           | Standard Accessories                  |      |

|           | Service Safety Summary                |      |

|           | Performance Check                     | 9-3  |

|           | Equipment List                        | 9-3  |

|           | Test Procedure Descriptions           |      |

|           | Troubleshooting                       |      |

|           | <del>y</del>                          |      |

|           | Diagnostics                           |      |

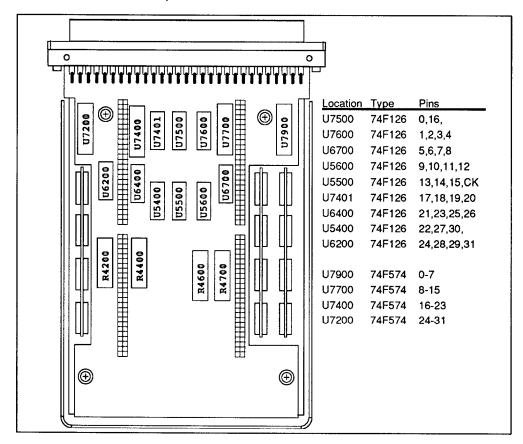

|           | Replacing Pin Driver and Receiver ICs |      |

|           | Module Removal/Replacement Procedure  | 9-12 |

|           | Removal                               |      |

|           | Replacement                           |      |

|           | Preparing the Module for Exchange     |      |

|           |                                       |      |

|           | Switch and Jumper Settings            |      |

|           | Replaceable Parts                     |      |

|           | Replaceable Parts List, Module        |      |

|           | Replaceable Parts List, Pod           | 9-14 |

|           |                                       |      |

Appendix A ASCII/GPIB Code Chart

Appendix B VXIbus Glossary

**Appendix C Fast Data Channel Reference**

Appendix D VX4820 Diagnostic Routines

## **GENERAL SAFETY SUMMARY**

Only qualified personnel should perform service procedures. This Service Safety Summary and the General Safety Summary should be read before performing service procedures.

The general safety information in this summary is for operating and servicing personnel. Specific warnings and cautions can be found throughout the manual where they apply, and may not appear in this summary.

#### TERMS IN THIS MANUAL

**CAUTION** statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### TERMS AS MARKED ON EQUIPMENT

**CAUTION** indicates a hazard to property, including the equipment itself, and could cause minor personal injury.

WARNING indicates a personal injury hazard not immediately accessible as you read the marking.

DANGER indicates a personal injury hazard immediately accessible as you read the marking.

#### SYMBOLS AS MARKED ON EQUIPMENT

DANGER-High voltage

Protective ground (earth) terminal.

ATTENTION-REFER TO MANUAL

#### GROUNDING THE PRODUCT

**WARNING:** This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, plug the power cord into a properly wired receptacle. A protective-ground connection by way of the grounding conductor in the power cord is essential for safe operation. (I.E.C. Safety Class I)

#### DANGER ARISING FROM LOSS OF GROUND

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulated) can render an electric shock.

#### **USE PROPER FUSE**

To avoid fire hazard use only a fuse of the correct type, voltage rating, and current rating.

#### REMOVE LOOSE OBJECTS

During disassembly or installation procedures, screws or other small objects may fall to the bottom of the mainframe. To avoid shorting out the power supply, do not power-up the instrument until such objects have been removed.

#### DO NOT OPERATE WITHOUT COVERS

To avoid personal injury or damage to the product, do not operate this product with the covers or panels removed.

#### **USE CARE WITH COVERS REMOVED**

To avoid personal injury, remove jewelry such as rings, watches, and other metallic objects before removing the cover. Do not touch exposed connections and components within the product while the power cord is connected.

#### REMOVE FROM OPERATION

If you have reason to believe that the instrument has suffered a component failure, do not operate the instrument until the cause of the failure has been determined and corrected.

#### DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specially certified for such operation.

#### SAFETY CERTIFICATION OF MODULES

For modules which are safety certified by Underwriters Laboratories, UL Listing applies only when the module is installed in a UL Listed product.

## **Purpose of this Document**

This manual provides the information necessary to install, configure, and operate the VX4820 Digital Test Module.

## Organization of this Manual

This manual consists of the following sections and appendices:

**Section 1. General Information** — Provides a brief overview of the VX4820 and its standard and optional accessories. This section also includes the VX4820 specifications.

**Section 2. Preparation for Use** — Provides information about how to configure and install the VX4820.

**Section 3. Operation and Programming** — Describes the connectors, the power-up sequence and module programming.

**Section 4.** Rear-Panel Interface — Describes the connectors on the VX4820 rear panel.

**Section 5. Command Notation and Formats** — Contains introductory information about the command dictionary.

**Section 6. Instrument Control Command Dictionary** — Contains an alphabetical and functional listing of the instrument control commands and a description of each command.

Section 7. System Command Dictionary — Contains information about the IEEE 488 commands.

Section 8. Digital Toolbox — Describes test development software.

**Section 9. Module Service** — Provide test and performance verification procedures.

Appendix A. ASCII and GPIB Code Chart

Appendix B. VXIbus Glossary

Appendix C. Fast Data Channel Reference

Appendix D. Diagnostic Tests

### **Notational Conventions**

#### **Active Signal States**

An asterisk (\*) following a signal mnemonic (as in ACFAIL\*) denotes the signal is active when in its low state.

A signal mnemonic without an asterisk (\*) denotes the signal is active when in its high state.

#### **Number Base**

Unless otherwise noted, all numbers are assumed to be decimal (base 10).

Binary numbers (base 2) are followed by the character "b" (for example: 1101b).

Hexadecimal numbers (base 16) are followed by the character "h" (for example: 97FFh).

Octal numbers (base 8) are followed by the character "o" (for example: 307o).

#### **Related Publications**

The following documents on related subjects may be useful for efficient use of the VX4820:

- VXIbus System Specification, Version 1.3, July 14, 1989

- VMEbus Specification Manual, Revision C.1, October, 1985

- ANSI/IEEE Standard 1014-1987, IEEE Standard for a Versatile Backplane Bus: VMEbus

# Section 1 General Information

## Introduction